This is part of the company’s ongoing work to build the Quantum Error Correction Stack that every quantum computer will need to achieve useful scale.

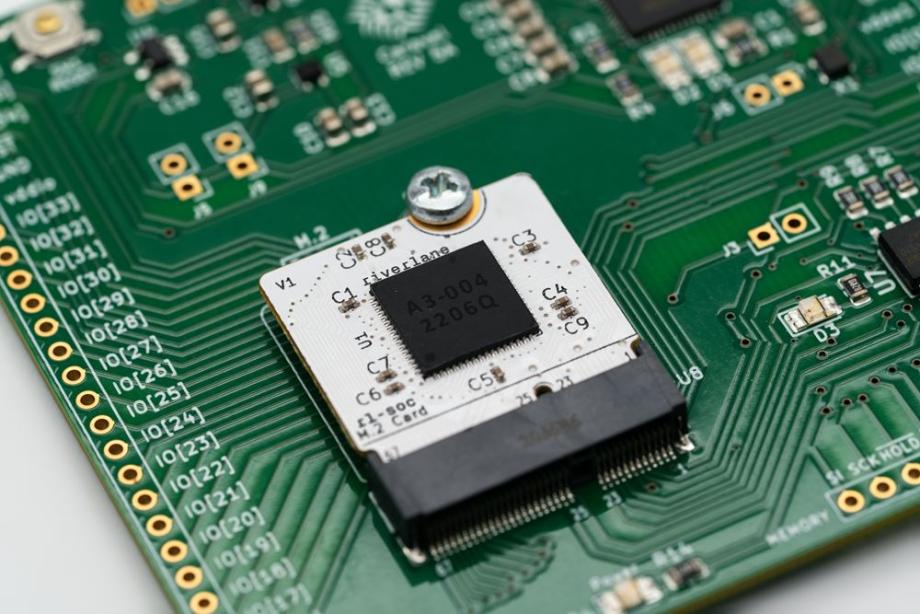

The application-specific integrated circuit (ASIC) demonstrator decoder chip is a critical element of this stack and the first of its kind to be fabricated. Riverlane has also published the IP for its more powerful next generation decoder and made this available to any quantum computer maker to use in its own hardware. Riverlane plans to demonstrate this decoder in live hardware in Q4 2023.

Quantum error correction is the defining challenge for quantum computers, allowing us to produce a large-scale quantum computer with error rates low enough for useful calculations.

To achieve this, we need a dedicated Quantum Error Correction Stack that sits between the quantum hardware and application layers. Every useful quantum computer, regardless of its qubit type and application, will need a Quantum Error Correction Stack.

There are many components in a Quantum Error Correction Stack. Riverlane is developing both the decoders and control systems that together turn many unreliable physical qubits into one more reliable ‘logical’ qubits. Quantum decoders must handle the terabytes of data produced by quantum computers every second to stop errors propagating and rendering calculations useless.

The ASIC chip – called DD0A - is the first release in the Decode ASIC Family, which delivers a high-speed, high-capacity and cost-effective decoder capable of operating at high volumes with significantly reduced power consumption.

Steve Brierley, CEO and founder of Riverlane, explained: "We’re entering a new era of quantum computing where we begin tackling the technology’s defining challenge – the need to scale from a few hundred quantum operations to a trillion quantum operations without failure. The only way to achieve this is via a complex new technology called quantum error correction. Riverlane is developing comprehensive technology to accelerate this transition for all quantum computers. Our launch of the world’s most powerful quantum decoder and the first ever decoding chip today are important steps in that journey."

Riverlane has also launched its Decode IP Family, which delivers real-time processing for error correction during runtime. It works with unprecedented speed and accuracy. The Decode IP Family is designed to be used with Field Programmable Gate Arrays (FPGAs), which allow for quick prototyping and integration, accelerating the speed of innovation.

Brierley added: "We are now implementing quantum algorithms on actual hardware. Crucially, Riverlane has found a balance to address all the metrics required to create a real-world decoder to solve real-world problems – making our decoder the most powerful decoder available."

Both the Decode ASIC Family and Decode IP Family can be integrated into superconducting, trapped ion and neutral atom quantum hardware. Riverlane will continue to develop and validate its next generations of its Decode ASIC Family and Decode IP Family.

Image credit: Riverlane.